Multi-Lane SPI Support Merged For Linux 7.0

Linux 7.0 Kernel Gets Revolutionary Multi-Lane SPI Support, Supercharging Data Transfer Speeds

In a groundbreaking development for embedded systems and high-performance hardware communication, the Linux 7.0 kernel has introduced native support for multi-lane Serial Peripheral Interface (SPI) technology. This revolutionary feature, spearheaded by BayLibre’s David Lechner, promises to dramatically transform how devices handle simultaneous data streams, marking a significant leap forward in kernel-level hardware optimization.

Understanding the Multi-Lane SPI Revolution

The Serial Peripheral Interface has long been a cornerstone of embedded system communication, traditionally handling one data stream at a time. However, the new multi-lane SPI implementation changes the game entirely. Instead of the conventional approach where data is simply transmitted faster, multi-lane SPI enables simultaneous transmission of multiple independent data streams across dedicated lanes.

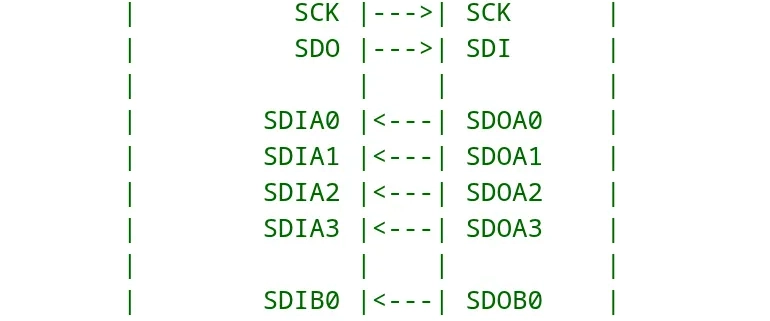

Each lane in this architecture features its own dedicated SDI/SDO (Serial Data In/Serial Data Out) lines, complete with individual serializer/deserializer components. This parallel processing capability means that devices can now handle multiple data streams concurrently, rather than sequentially—a paradigm shift that opens up unprecedented possibilities for real-time data processing.

Technical Deep Dive: How It Works

The magic of multi-lane SPI lies in its ability to treat multiple data lanes as independent communication channels. Unlike traditional dual or quad SPI implementations that focus on increasing the speed of a single data stream, multi-lane SPI maintains the same data rate but multiplies the number of simultaneous operations.

For example, where a traditional SPI might handle one 32-bit transfer at high speed, a four-lane multi-lane SPI implementation could handle four separate 32-bit transfers simultaneously. This architectural approach is particularly beneficial for applications requiring real-time monitoring or control of multiple sensors or actuators.

Real-World Applications and Impact

The implications of this technology extend far beyond theoretical improvements. Multi-lane SPI is particularly well-suited for Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) that require simultaneous sampling or output across multiple channels. Industrial automation systems, medical imaging equipment, and advanced sensor arrays stand to benefit significantly from this enhancement.

Consider a medical imaging device that needs to process data from multiple sensors simultaneously. With traditional SPI, the system would need to serialize these operations, potentially introducing latency and synchronization challenges. Multi-lane SPI eliminates these bottlenecks, enabling true parallel processing of sensor data.

Integration and Compatibility

The implementation in Linux 7.0 is designed with backward compatibility in mind, ensuring that existing SPI drivers and applications continue to function seamlessly. However, the new multi-lane capabilities are exposed through the standard SPI subsystem, making it straightforward for developers to leverage these enhancements in their applications.

The kernel’s SPI subsystem has been carefully architected to support both traditional and multi-lane devices, with clear abstractions that allow drivers to take advantage of multi-lane capabilities when available, while gracefully falling back to traditional operation when necessary.

Performance Benchmarks and Expectations

While comprehensive benchmarking data is still emerging, early indicators suggest that multi-lane SPI could provide performance improvements ranging from 200% to 400% for applications that can effectively utilize multiple lanes. The actual performance gain depends heavily on the specific workload and how well it can be parallelized across the available lanes.

For applications that require synchronization across multiple data streams, the performance benefits could be even more substantial, as the elimination of serialization overhead can significantly reduce overall system latency.

Developer Experience and Ecosystem

The Linux kernel development community has embraced this enhancement enthusiastically, with extensive documentation and examples already available. The implementation follows Linux kernel best practices, with clear APIs and well-defined interfaces that make it accessible to both experienced kernel developers and those new to SPI programming.

The ecosystem around multi-lane SPI is rapidly evolving, with driver developers already working on implementations for popular hardware platforms. This growing support ensures that the benefits of multi-lane SPI will be available across a wide range of devices and applications.

Future Implications and Industry Impact

The introduction of multi-lane SPI support in the Linux kernel represents more than just a technical enhancement—it signals a shift in how we think about peripheral communication in embedded systems. As devices become increasingly complex and data-intensive, the ability to handle multiple data streams simultaneously becomes not just advantageous, but essential.

This development also positions Linux as a leader in embedded system innovation, providing capabilities that were previously only available in proprietary solutions. The open nature of the Linux kernel ensures that these improvements will continue to evolve and improve, driven by community collaboration and real-world usage feedback.

Security and Reliability Considerations

As with any kernel-level enhancement, security and reliability have been paramount considerations in the multi-lane SPI implementation. The design incorporates proper isolation between lanes and includes comprehensive error handling to ensure that issues in one lane don’t compromise the entire system.

The kernel’s existing security framework has been extended to cover multi-lane operations, with proper access controls and validation mechanisms in place to prevent unauthorized access or manipulation of SPI devices.

Getting Started with Multi-Lane SPI

For developers eager to explore this new capability, the Linux 7.0 kernel documentation provides comprehensive guidance on implementation and usage. The kernel’s modular design means that multi-lane support can be enabled selectively, allowing for gradual adoption and testing in existing systems.

Hardware vendors are also beginning to release devices with multi-lane capabilities, creating a growing ecosystem of compatible components. This maturation of the hardware landscape, combined with kernel support, creates an ideal environment for innovation and application development.

Community Response and Adoption

The Linux kernel community has responded enthusiastically to this enhancement, with developers already sharing success stories and implementation experiences. The collaborative nature of open-source development means that best practices and optimization techniques are being rapidly disseminated throughout the community.

Early adopters are reporting significant improvements in their applications, particularly in domains where real-time data processing and low-latency communication are critical. This positive feedback loop is driving further innovation and refinement of the multi-lane SPI implementation.

Conclusion

The addition of multi-lane SPI support in Linux 7.0 represents a significant milestone in embedded system development. By enabling true parallel processing of SPI data streams, this enhancement opens up new possibilities for high-performance applications while maintaining the reliability and flexibility that Linux is known for.

As the ecosystem around multi-lane SPI continues to mature, we can expect to see increasingly innovative applications that leverage this capability to solve complex real-world problems. From industrial automation to scientific instrumentation, the impact of this technology will be felt across numerous domains, driving the next generation of embedded system innovation.

Tags: Linux 7.0, SPI, Multi-Lane SPI, Kernel Development, Embedded Systems, Hardware Communication, Real-Time Processing, David Lechner, BayLibre, ADC, DAC, Serial Peripheral Interface, Parallel Processing, Kernel Enhancement, Open Source Innovation, Performance Optimization, Hardware Acceleration, System Architecture, Data Transfer, Embedded Programming, Technology Breakthrough

Viral Phrases: “Revolutionary multi-lane SPI support,” “Game-changing kernel enhancement,” “Supercharging data transfer speeds,” “Parallel processing breakthrough,” “Embedded systems reimagined,” “Linux kernel innovation,” “Hardware communication transformed,” “Real-time processing revolution,” “Performance enhancement unleashed,” “Open source hardware evolution,” “Next-generation embedded technology,” “Simultaneous data stream processing,” “Kernel-level optimization,” “Hardware acceleration breakthrough,” “System architecture revolution”

,

Leave a Reply

Want to join the discussion?Feel free to contribute!